Introduction: Application-Specific Integrated Circuits (ASICs) are fundamental components in the realm of electronics, powering a vast array of devices from smartphones to industrial equipment. Synopsys Design Compiler is a leading-edge tool that facilitates the design, synthesis, and optimization of ASICs, enabling engineers to translate their hardware designs into efficient, high-performance integrated circuits. In this extensive guide, we’ll delve into the intricate world of ASIC design using Synopsys Design Compiler, covering everything from basic concepts to advanced optimization techniques.

Section 1: Understanding ASIC Design

1.1 Overview of ASICs: ASICs are custom-designed integrated circuits tailored to perform specific functions, offering advantages such as high performance, low power consumption, and compact form factor. ASIC design involves translating a hardware description into a physical circuit layout, optimizing for speed, power, area, and manufacturability.

1.2 Importance of ASIC Design: ASIC design is critical for achieving optimal performance and efficiency in electronic systems, especially in applications where off-the-shelf solutions are inadequate. ASICs offer customization, integration, and optimization benefits, enabling engineers to meet stringent requirements and differentiate their products in competitive markets.

1.3 Role of Synopsys Design Compiler: Synopsys Design Compiler is a comprehensive synthesis tool used by ASIC designers to transform hardware descriptions written in HDL (Hardware Description Language) into optimized gate-level netlists. It performs logic synthesis, technology mapping, optimization, and timing analysis, enabling designers to achieve high-quality ASIC designs with fast time-to-market.

Section 2: ASIC Design Flow Overview

2.1 Design Entry: The ASIC design flow begins with design entry, where engineers create and verify hardware descriptions using HDLs such as Verilog or VHDL. Designers define the functionality, architecture, and behavior of the ASIC using a combination of RTL (Register Transfer Level) code and behavioral models.

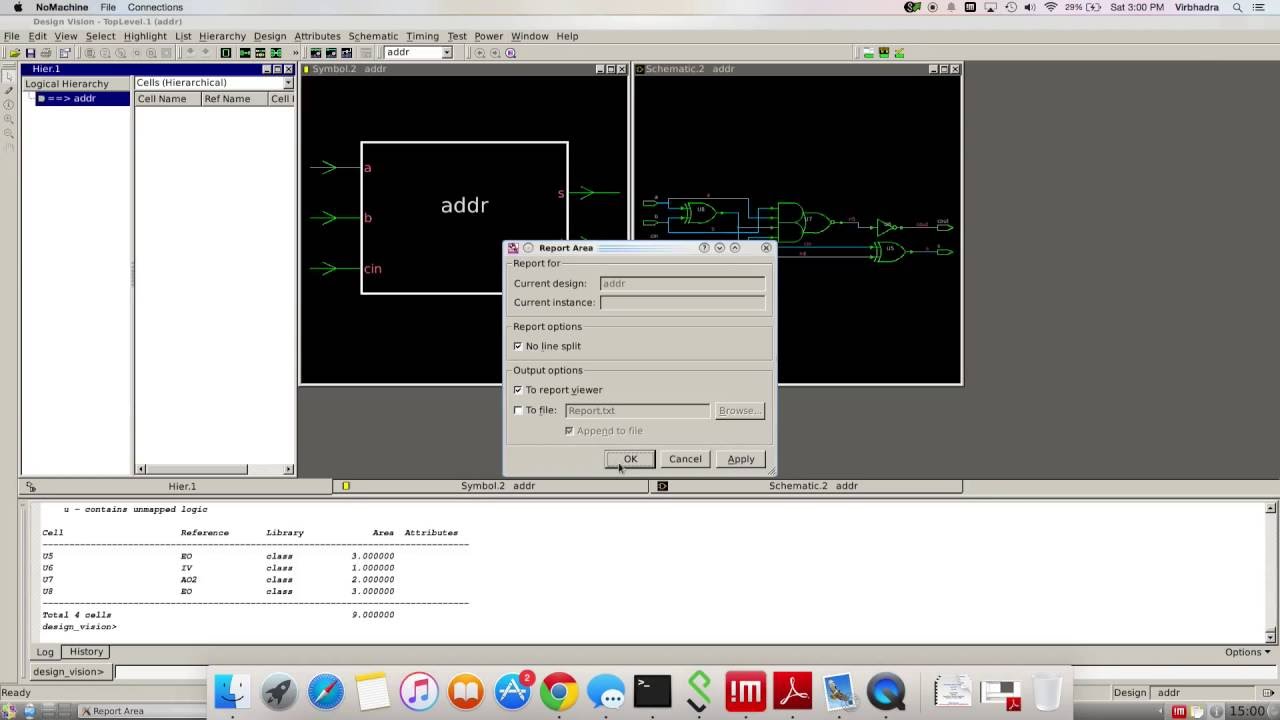

2.2 Synthesis and Optimization: Once the RTL design is complete, engineers use Synopsys Design Compiler to synthesize and optimize the design for the target technology node and performance goals. Design Compiler performs logic synthesis, technology mapping, optimization, and constraint-driven synthesis to generate an optimized gate-level netlist.

2.3 Verification and Validation: After synthesis, engineers perform verification and validation to ensure the correctness and functionality of the ASIC design. They use simulation tools, formal verification, and hardware emulation platforms to verify design behavior, functional correctness, and compliance with specifications.

2.4 Physical Design and Implementation: Following verification, engineers proceed to physical design and implementation, where they map the synthesized netlist onto the target FPGA or ASIC device. They perform floor planning, placement, routing, and timing closure to meet performance, area, and power constraints.

2.5 Post-Silicon Validation: Once the ASIC is fabricated, engineers conduct post-silicon validation to verify its performance, functionality, and reliability in real-world operating conditions. They perform electrical testing, characterization, and qualification to ensure that the ASIC meets design specifications and customer requirements.

Section 3: Using Synopsys Design Compiler for ASIC Design

3.1 Design Setup and Configuration: Engineers begin by setting up the design environment and configuring Synopsys Design Compiler for the target technology and design constraints. They specify synthesis options, optimization goals, design constraints, and target libraries to guide the synthesis process.

3.2 RTL-to-GDSII Flow: Design Compiler supports the entire RTL-to-GDSII (Graphical Design System II) flow, enabling engineers to synthesize, optimize, and implement ASIC designs from RTL to final layout. It seamlessly integrates with other Synopsys tools such as PrimeTime for timing analysis, IC Compiler for physical implementation, and StarRC for parasitic extraction.

3.3 Logic Synthesis and Optimization: Synopsys Design Compiler performs logic synthesis and optimization to translate RTL descriptions into gate-level netlists optimized for area, speed, and power. It applies a combination of optimization techniques such as logic restructuring, technology mapping, retiming, and register balancing to improve design quality and meet timing constraints.

3.4 Timing Analysis and Closure: Design Compiler includes timing analysis capabilities to analyze and optimize the timing performance of ASIC designs. Engineers use tools such as PrimeTime to perform static timing analysis, identify timing violations, and close timing paths through constraints, optimizations, and design modifications.

3.5 Power Optimization: Design Compiler offers power optimization features to reduce dynamic and static power consumption in ASIC designs. Engineers use techniques such as clock gating, power gating, voltage scaling, and multi-Vt optimization to minimize power dissipation while maintaining design performance and reliability.

Section 4: Advanced Techniques and Optimization Strategies

4.1 High-Level Synthesis (HLS): Synopsys Design Compiler supports high-level synthesis (HLS) to enable designers to explore architectural optimizations and trade-offs at a higher abstraction level. HLS tools such as Catapult Synthesis allow engineers to describe algorithms in C/C++ and automatically generate RTL code optimized for ASIC implementation.

4.2 Design Space Exploration: Design Compiler facilitates design space exploration to evaluate and compare alternative design implementations, architectures, and optimization strategies. Engineers use synthesis directives, constraints, and performance metrics to explore trade-offs in area, speed, power, and cost and select the optimal design solution.

4.3 Multi-Objective Optimization: Design Compiler enables multi-objective optimization to optimize ASIC designs for multiple conflicting goals simultaneously. Engineers define design constraints, objectives, and priorities using constraints files and optimization directives to balance trade-offs and achieve the best overall solution in terms of area, speed, power, and reliability.

Section 5: Best Practices and Tips

5.1 Hierarchical Design Methodology: Adopt a hierarchical design methodology to manage complexity, facilitate design reuse, and improve productivity in ASIC design projects. Divide the design into hierarchical modules, use abstraction layers, and establish clear interfaces to promote modularity, scalability, and collaboration among design teams.

5.2 Constraint-Driven Synthesis: Embrace constraint-driven synthesis to guide the synthesis process and achieve design goals efficiently. Define timing constraints, area constraints, power constraints, and design rules using Synopsys Design Constraints (SDC) files to constrain synthesis, optimization, and physical implementation.

5.3 Continuous Learning and Professional Development: Stay updated on the latest developments, methodologies, and best practices in ASIC design and synthesis. Participate in training programs, workshops, conferences, and user forums to enhance your proficiency in Synopsys Design Compiler, RTL design techniques, and synthesis methodologies.

Conclusion: Synopsys Design Compiler is a powerful tool that empowers ASIC designers to synthesize, optimize, and implement high-quality ASIC designs with speed, efficiency, and reliability. By mastering the fundamentals, methodologies, and advanced techniques discussed in this guide, designers can leverage Design Compiler to achieve their design goals, meet performance targets, and deliver innovative ASIC solutions for a wide range of applications. With its comprehensive features, robust optimization algorithms, and seamless integration with industry-standard tools, Design Compiler enables designers to push the boundaries of ASIC design and drive innovation in electronic design automation.